回路・システムグループ

超高速・高時間分解能CMOSイメージセンサ

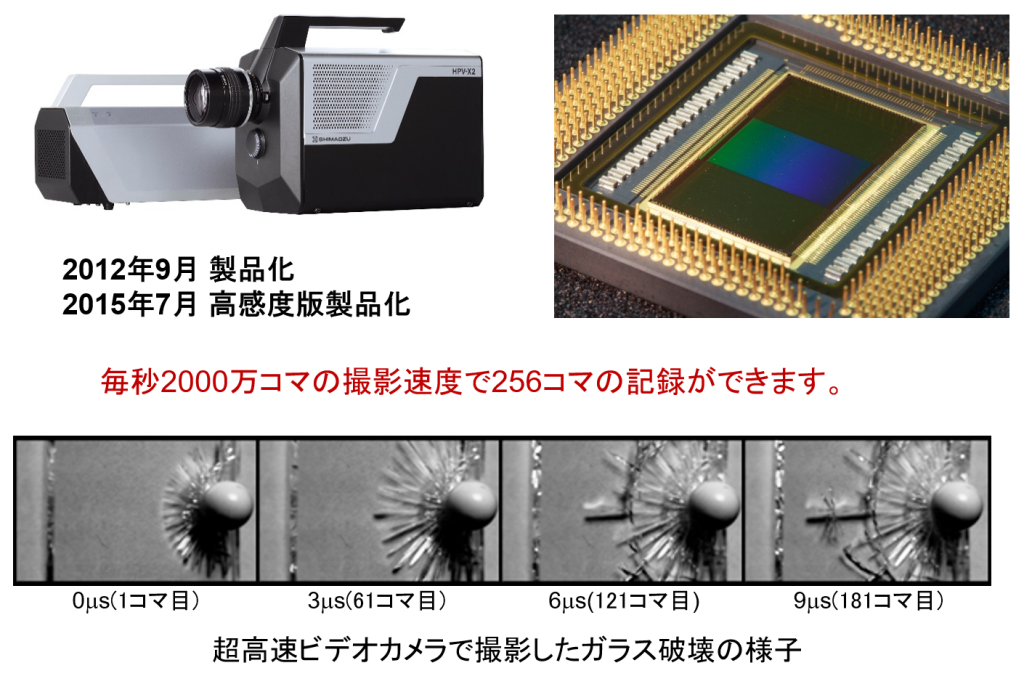

画素アレイとメモリアレイを1チップ上に分離配置し、画素毎に複数のメモリを接続した構造を新開発することにより、撮影速度・記録コマ数・画素数を両立させた世界最高性能のイメージセンサを実現しました。

研究室で開発された高速ビデオカメラは2012年に初めて製品化され、改良を重ねて大幅に高感度化したカメラが2015年7月に製品化されました。現在はさらなる性能向上を目指し、毎秒1億コマを超える高速化や多画素化へ向けた研究に取り組んでいます。

また、超高速センサの技術を応用した高時間分解能センサと距離イメージングの研究も行っています。

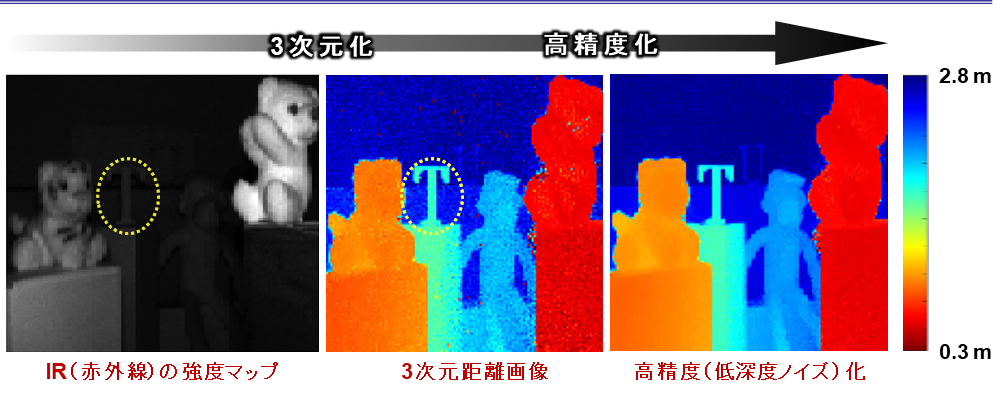

3次元CMOSイメージセンサ

様々な分野でIoT化や自動化が推し進められており、これらのマシンビジョン応用のためには従来の2次元画像に加え、距離情報を含む3次元画像の取得が求められています。この需要に対応すべく、本研究グループでは赤外光源を利用したiToF方式CMOSイメージセンサによって3次元測距を行っています。

また当研究室がこれまでに培ってきた高速電荷転送技術や、高容量なトレンチキャパシタを利用することで、より高精度(低深度ノイズ)・より高速(高フレームレート)な距離測定を目指しています.

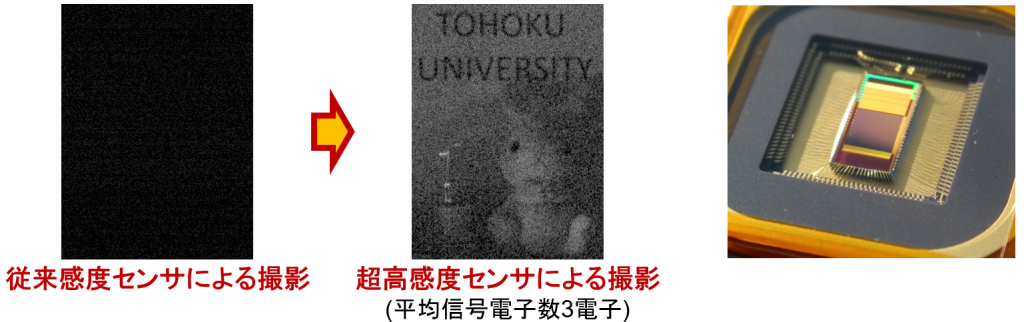

高感度・広ダイナミックレンジCMOSイメージセンサ

イメージセンサの各画素内にフォトダイオードから溢れた光電荷を蓄積する容量を追加することで、一回の露光で強い光から微弱光までを捉えることができるイメージセンサを創出し、2008年より防犯カメラ等で実用化され、安心安全な社会の実現に貢献しています。

この技術を発展させて、現在は、強い光を犠牲にすることなく、高感度化の物理限界である光子1つ1つを計測するフォトンカウンティング感度を実現する、極限を目指したイメージセンサ技術とその応用研究の開発を行っています。

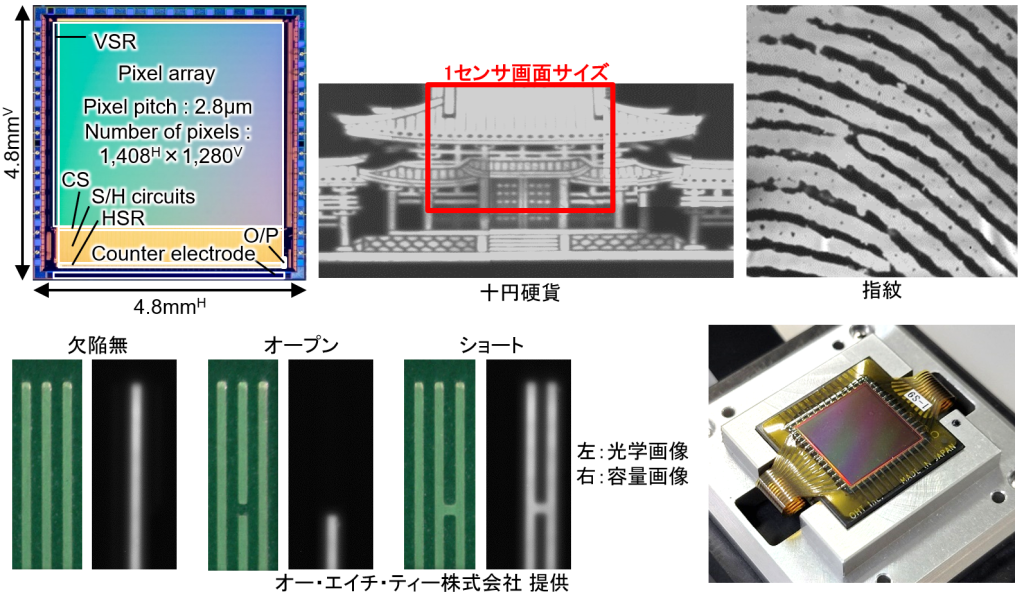

近接容量CMOSイメージセンサ

CMOSイメージセンサの低ノイズ信号読み出し技術を応用し、センサ近傍に形成される静電容量の2次元分布を可視化するイメージセンサを開発しています。透明電極やnmオーダーの凹凸など、光学イメージセンサでは見ることが難しい対象物も、このセンサを用いることで見ることが出来ます。また、配線のオープン/ショート欠陥の可視化も可能です。

現在は、ディスプレイ検査装置や高精度圧力計等への応用に向けて実証実験を行っています。また、チップ性能のさらなる向上とセンサの製品化に向けた技術開発を進めています。

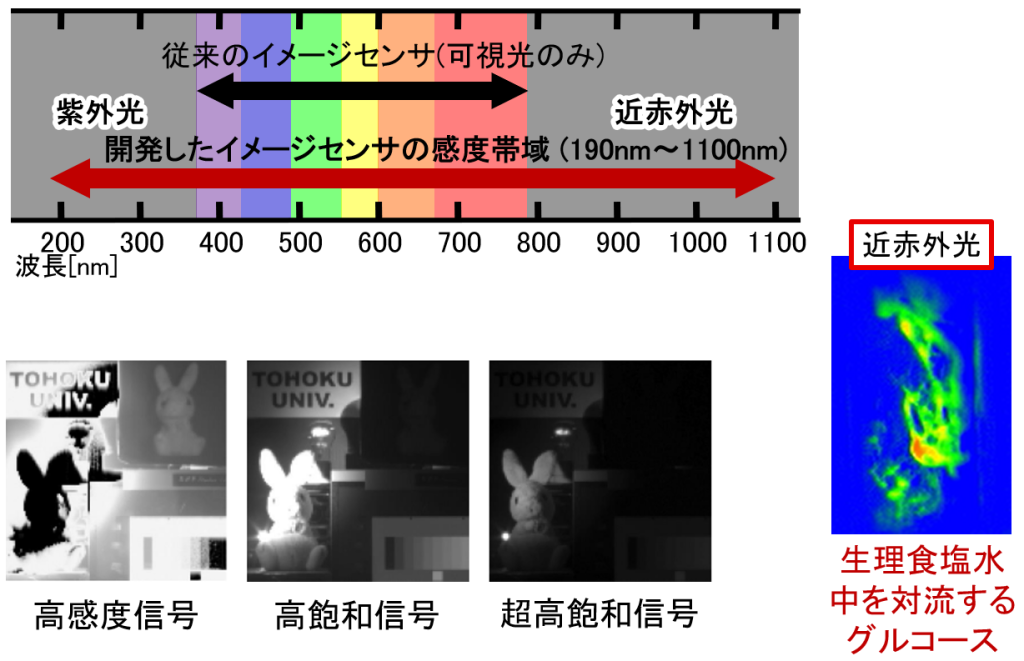

高飽和・広光波長帯域CMOSイメージセンサ

画素毎に高い飽和信号量を実現することでわずかな吸光等による微小光信号変化を高い精度で捉えると共に、人の目には見えない紫外光から近赤外光までの光情報を可視化できるイメージセンサを開発しています。血管中の血液成分やその流れを可視化することで、非侵襲血糖値測定などへの応用が期待されます。また、開発技術では、明暗差の激しい被写体を単一露光で撮像可能です。

現在は、チップ性能のさらなる向上やスマートな信号読み出しによる機能拡大に向けた技術開発を進めております。これらの技術を用いたセンシング技術は、車載、認証認識、製造業、農業、医療など、幅広い分野への応用が期待されています。

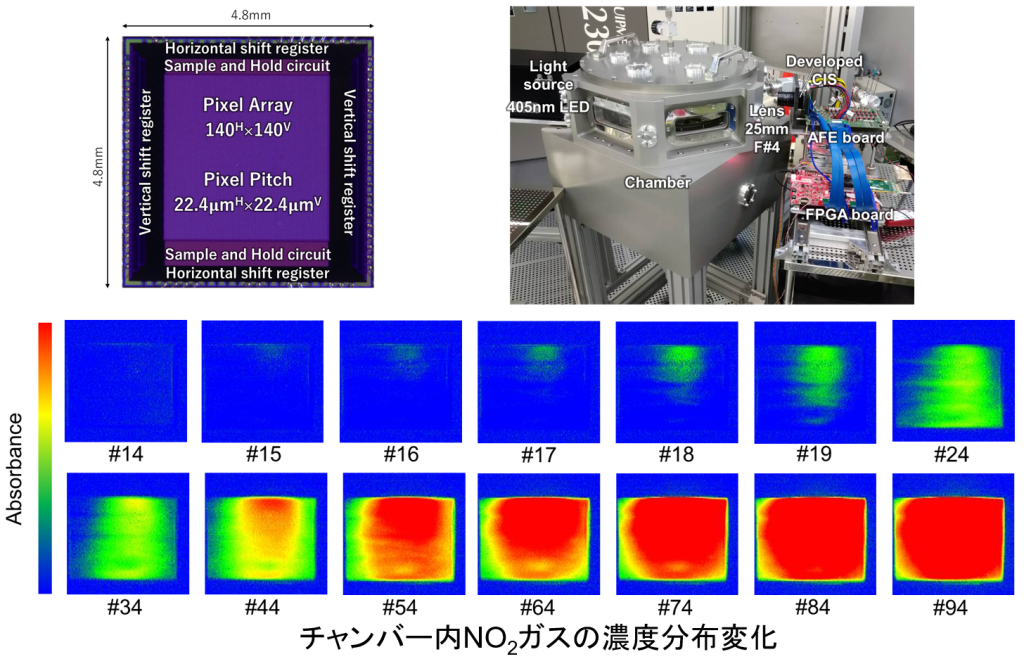

流体濃度分布可視化CMOSイメージセンサ

強い光や幅広い光波長においても撮像を可能とする技術に加え、動く被写体に対してもブレや歪みの少ない高速グローバルシャッタ方式を導入したセンサを開発しています。

この技術を応用してガスや気体による光の吸収をイメージングし、リアルタイムに流体の濃度分布の可視化する技術の創出に取り組んでいます。

本技術は半導体製造チャンバー内のガス分布や農作物の品質、河川や大気における有害物質の可視化・測定等への応用が期待されています。

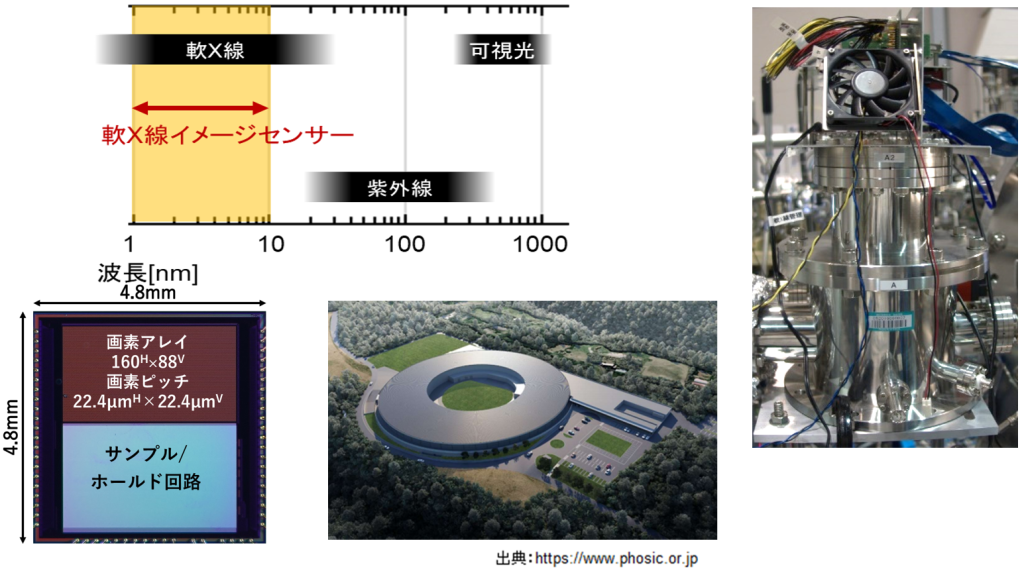

軟X線検出CMOSイメージセンサ

表面に薄く急峻な不純物濃度プロファイルを適応したSiフォトダイオード技術を用い、紫外光から近赤外光までの光情報を画像化するイメージセンサ技術を開発しました。

この技術を応用・発展させて、波長が紫外線よりも短い軟X線を検出する裏面照射型のCMOSイメージセンサを開発しています。導入技術の原理確認用に開発したセンサチップでは概ね良好な特性が確認出来ています。

現在は、改良を加えながら東北大青葉山キャンパスに建設中の次世代放射光施設での利用を目指した大判のセンサチップの開発や更なる発展版の開発を進めています。

デバイス・プロセスグループ

〇 半導体製造の特徴

身の回りの電子機器のほとんどは半導体集積回路(IC)によって構成され動作します。イメージセンサなどの半導体集積回路は、様々な工程(プロセス)を経て製造されます。

半導体基板上に微細な素子や回路を作り込むには、パターンを形成するリソ工程、材料膜を形成する成膜工程、材料膜を削るエッチング工程など、膨大な数の工程が必要になります。また、最先端の量産現場では数nmと原子レベルのサイズで複雑な回路を形成することに加え、一度に大量のチップを製造します。そのため、半導体製造プロセスでは良品が得られる割合である歩留りや、特性の誤差を考慮するばらつきといった考えが非常に重要になります。

デバイス・プロセスグループでは、半導体製造の考えに基づき、ばらつき原因の解明、新デバイス開発などの研究に取り組んでいます。

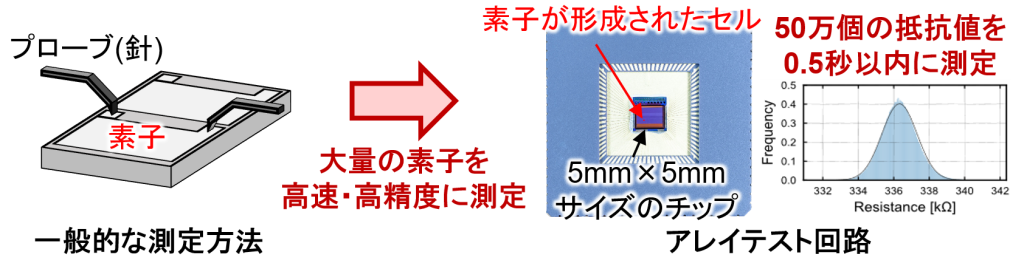

アレイテスト回路

より良い半導体集積回路を創出するには、半導体素子のノイズ・ばらつきを含めた電気的特性の評価が必要不可欠です。一般的な測定方法では素子1個ずつにプローブ(針)を当てて測定することから、大量の素子を測定しようとすると長い時間がかかってしまいます。

そこで、我々の研究グループでは大量の素子の高速・高精度な測定および統計的な解析を実現するために、アレイテスト回路の開発に取り組んでいます。アレイテスト回路はCMOSイメージセンサの読み出し技術を応用展開することで、アレイ状に並んだ大量の素子を高速・高精度に測定することができます。抵抗・電流などの特性を測定できるアレイテスト回路を設計・測定し、統計的な視点で未知の特性の原因解析を目指しています。

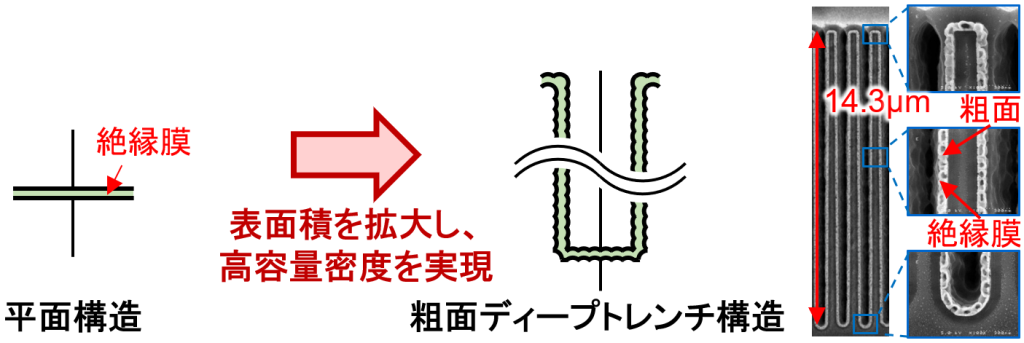

粗面ディープトレンチキャパシタ

キャパシタ(コンデンサ)は電荷を蓄え放出することができる受動素子であり、身の周りのほとんどの電子デバイスに使用されています。構造自体は電極の間に絶縁膜を形成するシンプルなものですが、小面積で大容量を実現するために様々な技術が開発されています。

本研究では、表面を凸凹にする粗面技術とSi基板に深い溝を掘るディープトレンチ構造の融合によって表面積を飛躍的に拡大し、今までにない高容量密度を実現するキャパシタ開発に取り組んでいます。

現在では、このキャパシタ技術をCMOSイメージセンサやアレイテスト回路などに導入する技術の開発を進めています。